搜索到53條【FPGA開發(fā)板】相關(guān)的全部。

搜索到53條【FPGA開發(fā)板】相關(guān)的全部。

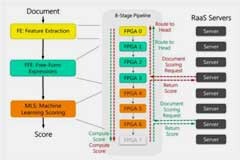

數(shù)據(jù)中心加速芯片需求大爆發(fā),F(xiàn)PGA正領(lǐng)跑市場

FPGA數(shù)據(jù)中心 2022-12-29 10:48

FPGA數(shù)據(jù)中心 2022-12-29 10:48

加載更多

查看關(guān)鍵詞的分類頻道

查看關(guān)鍵詞的分類頻道