搜索到7條【移植到FPGA】相關(guān)的技術(shù)文章。

搜索到7條【移植到FPGA】相關(guān)的技術(shù)文章。

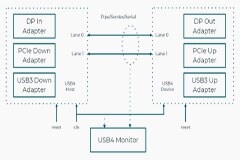

將ASIC IP核移植到FPGA上——如何確保性能與時序以完成充滿挑戰(zhàn)的任務(wù)!

數(shù)字芯片設(shè)計 ASIC IP FPGA 2024-8-26 11:52

數(shù)字芯片設(shè)計 ASIC IP FPGA 2024-8-26 11:52

加載更多

查看關(guān)鍵詞的分類頻道

查看關(guān)鍵詞的分類頻道